## Dae-Hyun Kim

List of Publications by Year in descending order

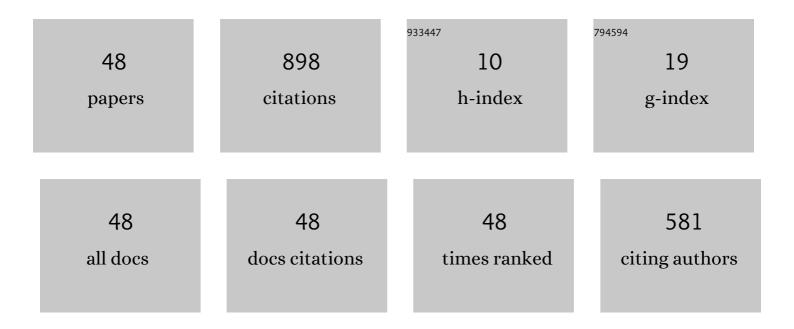

Source: https://exaly.com/author-pdf/7564357/publications.pdf Version: 2024-02-01

DAF-HVIIN KIM

| #  | Article                                                                                                                                                                                                                                      | IF  | CITATIONS |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 1  | AVATAR: A Variable-Retention-Time (VRT) Aware Refresh for DRAM Systems. , 2015, , .                                                                                                                                                          |     | 144       |

| 2  | Fast and Accurate Analytical Modeling of Through-Silicon-Via Capacitive Coupling. IEEE Transactions on Components, Packaging and Manufacturing Technology, 2011, 1, 168-180.                                                                 | 2.5 | 71        |

| 3  | Architectural Support for Mitigating Row Hammering in DRAM Memories. IEEE Computer Architecture<br>Letters, 2015, 14, 9-12.                                                                                                                  | 1.5 | 71        |

| 4  | Study of Through-Silicon-Via Impact on the 3-D Stacked IC Layout. IEEE Transactions on Very Large<br>Scale Integration (VLSI) Systems, 2013, 21, 862-874.                                                                                    | 3.1 | 70        |

| 5  | Design method and test structure to characterize and repair TSV defect induced signal degradation in 3D system. , 2010, , .                                                                                                                  |     | 55        |

| 6  | An 80 nm 4 Gb/s/pin 32 bit 512 Mb GDDR4 Graphics DRAM With Low Power and Low Noise Data Bus<br>Inversion. IEEE Journal of Solid-State Circuits, 2008, 43, 121-131.                                                                           | 5.4 | 54        |

| 7  | Design and Analysis of 3D-MAPS (3D Massively Parallel Processor with Stacked Memory). IEEE Transactions on Computers, 2015, 64, 112-125.                                                                                                     | 3.4 | 52        |

| 8  | Pre-Bond and Post-Bond Test and Signal Recovery Structure to Characterize and Repair TSV Defect<br>Induced Signal Degradation in 3-D System. IEEE Transactions on Components, Packaging and<br>Manufacturing Technology, 2011, 1, 1718-1727. | 2.5 | 50        |

| 9  | A 7 Gb/s/pin 1 Gbit GDDR5 SDRAM With 2.5 ns Bank to Bank Active Time and No Bank Group Restriction.<br>IEEE Journal of Solid-State Circuits, 2011, 46, 107-118.                                                                              | 5.4 | 29        |

| 10 | ArchShield. Computer Architecture News, 2013, 41, 72-83.                                                                                                                                                                                     | 2.5 | 29        |

| 11 | Analysis of TSV-to-TSV coupling with high-impedance termination in 3D ICs. , 2011, , .                                                                                                                                                       |     | 28        |

| 12 | Block-level 3D IC design with through-silicon-via planning. , 2012, , .                                                                                                                                                                      |     | 25        |

| 13 | Backend low-k TDDB chip reliability simulator. , 2011, , .                                                                                                                                                                                   |     | 20        |

| 14 | A 60nm 6Gb/s/pin GDDR5 Graphics DRAM with Multifaceted Clocking and ISI/SSN-Reduction Techniques. , 2008, , .                                                                                                                                |     | 19        |

| 15 | Impact of nano-scale through-silicon vias on the quality of today and future 3D IC designs. , 2011, , .                                                                                                                                      |     | 18        |

| 16 | A 40nm 2Gb 7Gb/s/pin GDDR5 SDRAM with a programmable DQ ordering crosstalk equalizer and adjustable clock-tracking BW. , 2011, , .                                                                                                           |     | 18        |

| 17 | Design Quality Trade-Off Studies for 3-D ICs Built With Sub-Micron TSVs and Future Devices. IEEE Journal on Emerging and Selected Topics in Circuits and Systems, 2012, 2, 240-248.                                                          | 3.6 | 17        |

| 18 | 22.2 An 8.5Gb/s/pin 12Gb-LPDDR5 SDRAM with a Hybrid-Bank Architecture using Skew-Tolerant,<br>Low-Power and Speed-Boosting Techniques in a 2nd generation 10nm DRAM Process. , 2020, , .                                                     |     | 14        |

Dae-Hyun Kim

| #  | Article                                                                                                                                                                                                                                       | IF  | CITATIONS |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 19 | Built-In Self-Test Methodology With Statistical Analysis for Electrical Diagnosis of Wearout in a<br>Static Random Access Memory Array. IEEE Transactions on Very Large Scale Integration (VLSI) Systems,<br>2016, 24, 2521-2534.             | 3.1 | 10        |

| 20 | Front-end of line and middle-of-line time-dependent dielectric breakdown reliability simulator for logic circuits. Microelectronics Reliability, 2017, 76-77, 81-86.                                                                          | 1.7 | 9         |

| 21 | Backend Dielectric Reliability Full Chip Simulator. IEEE Transactions on Very Large Scale Integration<br>(VLSI) Systems, 2014, 22, 1750-1762.                                                                                                 | 3.1 | 7         |

| 22 | Design quality tradeoff studies for 3D ICs built with nano-scale TSVs and devices. , 2012, , .                                                                                                                                                |     | 6         |

| 23 | ECC-ASPIRIN: An ECC-assisted post-package repair scheme for aging errors in DRAMs. , 2016, , .                                                                                                                                                |     | 6         |

| 24 | A 40nm 7Gb/s/pin single-ended transceiver with jitter and ISI reduction techniques for high-speed DRAM interface. , 2010, , .                                                                                                                 |     | 5         |

| 25 | TSV density-driven global placement for 3D stacked ICs. , 2011, , .                                                                                                                                                                           |     | 5         |

| 26 | Built-in self-test for bias temperature instability, hot-carrier injection, and gate oxide breakdown in embedded DRAMs. Microelectronics Reliability, 2015, 55, 2113-2118.                                                                    | 1.7 | 5         |

| 27 | Memory yield and lifetime estimation considering aging errors. , 2015, , .                                                                                                                                                                    |     | 5         |

| 28 | An ECC-Assisted Postpackage Repair Methodology in Main Memory Systems. IEEE Transactions on Very<br>Large Scale Integration (VLSI) Systems, 2017, 25, 2045-2058.                                                                              | 3.1 | 5         |

| 29 | Optimization of Experimental Designs for System- Level Accelerated Life Test in a Memory System<br>Degraded by Time-Dependent Dielectric Breakdown. IEEE Transactions on Very Large Scale Integration<br>(VLSI) Systems, 2019, 27, 1640-1651. | 3.1 | 5         |

| 30 | An 80nm 4Gb/s/pin 32b 512Mb GDDR4 Graphics DRAM with Low-Power and Low-Noise Data-Bus Inversion. , 2007, , .                                                                                                                                  |     | 4         |

| 31 | Global bus route optimization with application to microarchitectural design exploration. , 2008, , .                                                                                                                                          |     | 4         |

| 32 | A 7Gb/s/pin GDDR5 SDRAM with 2.5ns bank-to-bank active time and no bank-group restriction. , 2010, , .                                                                                                                                        |     | 4         |

| 33 | Impact of through-silicon-via scaling on the wirelength distribution of current and future 3D ICs. , 2011, , .                                                                                                                                |     | 4         |

| 34 | Block-level designs of die-to-wafer bonded 3D ICs and their design quality tradeoffs. , 2013, , .                                                                                                                                             |     | 4         |

| 35 | The die-to-die calibrated combined model of negative bias temperature instability and gate oxide breakdown from device to system. Microelectronics Reliability, 2015, 55, 1404-1411.                                                          | 1.7 | 4         |

| 36 | An 8.5-Gb/s/Pin 12-Gb LPDDR5 SDRAM With a Hybrid-Bank Architecture, Low Power, and Speed-Boosting<br>Techniques. IEEE Journal of Solid-State Circuits, 2021, 56, 212-224.                                                                     | 5.4 | 4         |

**DAE-HYUN KIM**

| #  | Article                                                                                                                                                                                     | IF  | CITATIONS |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 37 | AVERT: An elaborate model for simulating variable retention time in DRAMs. Microelectronics Reliability, 2015, 55, 1313-1319.                                                               | 1.7 | 3         |

| 38 | TDDB-emerald: A methodology for estimating memory reliability degradation resulting from time-dependent dielectric breakdown. , 2016, , .                                                   |     | 3         |

| 39 | Impact of die partitioning on reliability and yield of 3D DRAM. , 2014, , .                                                                                                                 |     | 2         |

| 40 | Analysis of errors in estimating wearout characteristics of time-dependent dielectric breakdown using system-level accelerated life test. Microelectronics Reliability, 2017, 76-77, 47-52. | 1.7 | 2         |

| 41 | Memory reliability estimation degraded by TDDB using circuit-level accelerated life test. , 2017, , .                                                                                       |     | 2         |

| 42 | Optimal Accelerated Test Regions for Time- Dependent Dielectric Breakdown Lifetime Parameters<br>Estimation in FinFET Technology. , 2018, , .                                               |     | 2         |

| 43 | Fabrication of mems structure with nano-gap using photo-assisted electrochemical etching. , 0, , .                                                                                          |     | 1         |

| 44 | TDDB chip reliability in copper interconnects. , 2010, , .                                                                                                                                  |     | 1         |

| 45 | Design for reliability: A duty-cycle management system for timing violations. , 2016, , .                                                                                                   |     | 1         |

| 46 | A methodology for estimating memory lifetime using a system-level accelerated life test and error-correcting codes. , 2017, , .                                                             |     | 1         |

| 47 | Fabrication of nano-gap accelerometer using photo-assisted electrochemical etching. , 0, , .                                                                                                |     | 0         |

| 48 | Bus-aware microarchitectural floorplanning. , 2008, , .                                                                                                                                     |     | 0         |

4