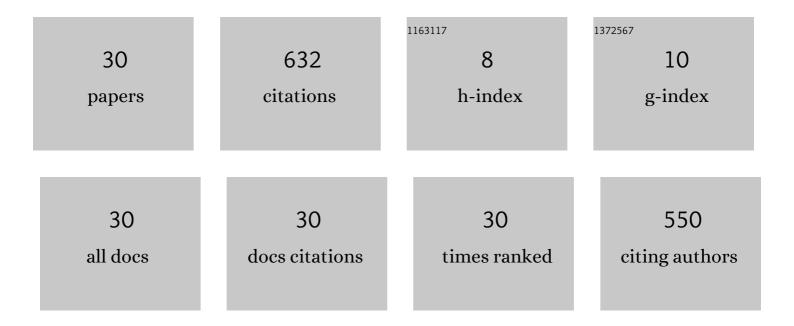

## James C Hoe

List of Publications by Year in descending order

Source: https://exaly.com/author-pdf/6846596/publications.pdf

Version: 2024-02-01

IMMES C HOE

| #  | Article                                                                                                                                                                | IF   | CITATIONS |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|

| 1  | Processor Assisted Worklist Scheduling for FPGA Accelerated Graph Processing on a Shared-Memory Platform. , 2019, , .                                                  |      | 15        |

| 2  | High-Performance Memory Snapshotting for Real-Time, Consistent, Hypervisor-Based Monitors. IEEE<br>Transactions on Dependable and Secure Computing, 2019, , 1-1.       | 5.4  | 3         |

| 3  | PageRank Acceleration for Large Graphs with Scalable Hardware and Two-Step SpMV. , 2018, , .                                                                           |      | 12        |

| 4  | SPIRAL: Extreme Performance Portability. Proceedings of the IEEE, 2018, 106, 1935-1968.                                                                                | 21.3 | 58        |

| 5  | FFTs with Near-Optimal Memory Access Through Block Data Layouts: Algorithm, Architecture and Design Automation. Journal of Signal Processing Systems, 2016, 85, 67-82. | 2.1  | 8         |

| 6  | FFTS with near-optimal memory access through block data layouts. , 2014, , .                                                                                           |      | 6         |

| 7  | Algorithm/hardware co-optimized SAR image reconstruction with 3D-stacked logic in memory. , 2014, , .                                                                  |      | 3         |

| 8  | HAMLeT: Hardware accelerated memory layout transform within 3D-stacked DRAM. , 2014, , .                                                                               |      | 11        |

| 9  | Memory Bandwidth Efficient Two-Dimensional Fast Fourier Transform Algorithm and Implementation for Large Problem Sizes. , 2012, , .                                    |      | 24        |

| 10 | Computer Generation of Hardware for Linear Digital Signal Processing Transforms. ACM Transactions on Design Automation of Electronic Systems, 2012, 17, 1-33.          | 2.6  | 97        |

| 11 | Optimizing FFT Precision in Optical OFDM Transceivers. IEEE Photonics Technology Letters, 2011, 23, 1550-1552.                                                         | 2.5  | 17        |

| 12 | Automatic Pipelining From Transactional Datapath Specifications. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2011, 30, 441-454.     | 2.7  | 20        |

| 13 | Predistortion and OFDM realizations. , 2011, , .                                                                                                                       |      | 0         |

| 14 | Hardware implementation of the discrete fourier transform with non-power-of-two problem size. ,<br>2010, , .                                                           |      | 12        |

| 15 | Design studies for an ASIC implementation of an optical OFDM transceiver. , 2010, , .                                                                                  |      | 9         |

| 16 | Optical OFDM for the data center. , 2010, , .                                                                                                                          |      | 28        |

| 17 | Real-time DSP-based optical OFDM transmission. , 2010, , .                                                                                                             |      | 1         |

| 18 | High Performance Stereo Vision Designed for Massively Data Parallel Platforms. IEEE Transactions on<br>Circuits and Systems for Video Technology, 2010, 20, 1509-1519. | 8.3  | 40        |

JAMES C HOE

| #  | Article                                                                                                                                                                        | IF  | CITATIONS |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| 19 | High-Level Design and Validation of the BlueSPARC Multithreaded Processor. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2010, 29, 1459-1470. | 2.7 | 12        |

| 20 | Automatic generation of streaming datapaths for arbitrary fixed permutations. , 2009, , .                                                                                      |     | 13        |

| 21 | Permuting streaming data using RAMs. Journal of the ACM, 2009, 56, 1-34.                                                                                                       | 2.2 | 44        |

| 22 | FPGA-based optical transmitters for electronic predistortion and advanced signal format generation. , 2009, , .                                                                |     | 0         |

| 23 | MEMOCODE 2006 guest editors' introduction. Design Automation for Embedded Systems, 2008, 12, 95-95.                                                                            | 1.0 | 0         |

| 24 | Formal datapath representation and manipulation for implementing DSP transforms. , 2008, , .                                                                                   |     | 36        |

| 25 | Domain-specific library generation for parallel software and hardware platforms. , 2008, , .                                                                                   |     | 11        |

| 26 | Generating FPGA-Accelerated DFT Libraries. , 2007, , .                                                                                                                         |     | 23        |

| 27 | Time-Multiplexed Multiple-Constant Multiplication. IEEE Transactions on Computer-Aided Design of<br>Integrated Circuits and Systems, 2007, 26, 1551-1563.                      | 2.7 | 67        |

| 28 | FFT Compiler: from math to efficient hardware HLDVT invited short paper. , 2007, , .                                                                                           |     | 0         |

| 29 | Fast and accurate resource estimation of automatically generated custom DFT IP cores. , 2006, , .                                                                              |     | 19        |

|    |                                                                                                                                                                                |     |           |

30 Automatic generation of customized discrete fourier transform IPs. , 2005, , .

43